|

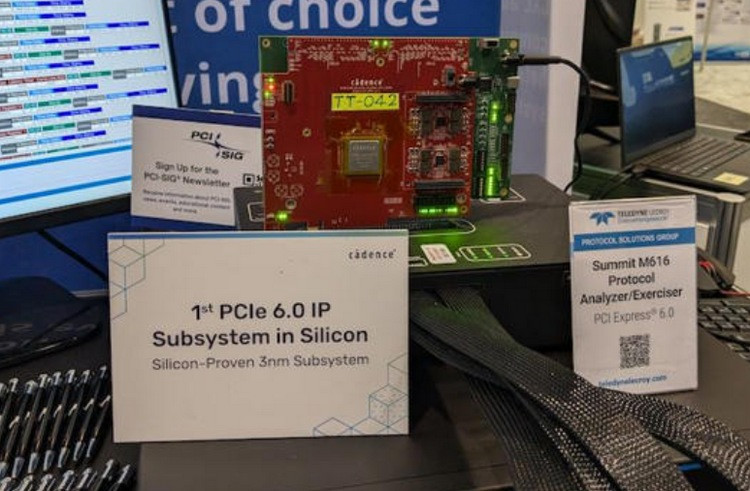

随着 PCIe 5.0 SSD 在数据中心和消费市场部署加速,PCI-SIG 联盟开始加速推进下下一代 PCIe 7.0 方案,尽管 PCIe 6.0 产品还未出货。 在最近的 FMS 2024 闪存技术峰会上,有供应商已经开始讨论具有 128 GT/s 带宽的 PCIe 7.0。PCI-SIG 已经向其成员提供了 PCIe 7.0 规范(0.5 版),预计完整规范将于 2025 年正式发布。  PCIe 7.0 使用 x16 通道,能提供 128 GT/s 超高带宽,支持高达 512 GBps 的双向流量。值得一提的是,PCIe 7.0 保留了 PAM4 信号并保持向后兼容性。这跟 6.0方案一样,这比当下PCIE 5.0和4.0 方案采用的 NRZ 信号指令有更高的误码率。因此,从PCIe 6.0 开始,将采用不同的纠错方案,流量控制单元 (FLIT) 编码不是在可变长度的数据包上运行,而是在固定大小的数据包上运行,以帮助前向纠错。  说回来,PCIe 6.0 的首个样品已经顺利在 FMS 2024 大会上点亮,采用3nm 芯片,没有透露性能,但官方表示符合 PCIe 6.0 性能规范。  最后,PCI-SIG 联盟看好 OCuLink 接口,目前已成为不少迷你主机的卖点,能外接高端显卡和扩展坞等。随着性能继续改进,预计会成为非常重要的扩展接口。

|  310112100042806

310112100042806